Prezados Professores, Pesquisadores e Alunos da área de Microeletrônica/Nanoeletrônica,

Gostaríamos de convida-los para participar de mais uma escola de microeletrônica que ocorrerá em São Paulo (EMICRO-SP) intitulada:

OFICINA USP DE FABRICAÇÃO DE CIRCUITOS INTEGRADOS MOS (TECNOLOGIA SOI nMOSFET de 0.5mm)

Local:

Laboratório de Microeletrônica (LME)

Laboratório de Sistemas Integráveis (LSI)

Depto de Sistemas Eletrônicos (PSI) da Escola Politécnica da USP

Data: 24 a 28/07/2017 (40 horas)

Número de vagas: 12

Inscrição Gratuita

Data máxima de inscrição: 31/05/2017

Inscrição e informações adicionais diretamente pelo site abaixo:

www.psi.poli.usp.br/emicro-fabricacao

Contato/dúvidas:

Prof. Dr. João A. Martino

email: martino@usp.br

Prof. Dr. Marcelo N. P. Carreno

email: carreno@lme.usp.br

Ms. Ricardo Rangel

Email: rrangel@lsi.usp.br

Departamento de Sistemas Eletrônicos (PSI)

Escola Politécnica da USP

Informações adicionais sobre o curso pode ser visto no folder anexo e no site acima indicado, reproduzido parcialmente abaixo.

——————————————————————————————————–

ESCOPO DO CURSO:

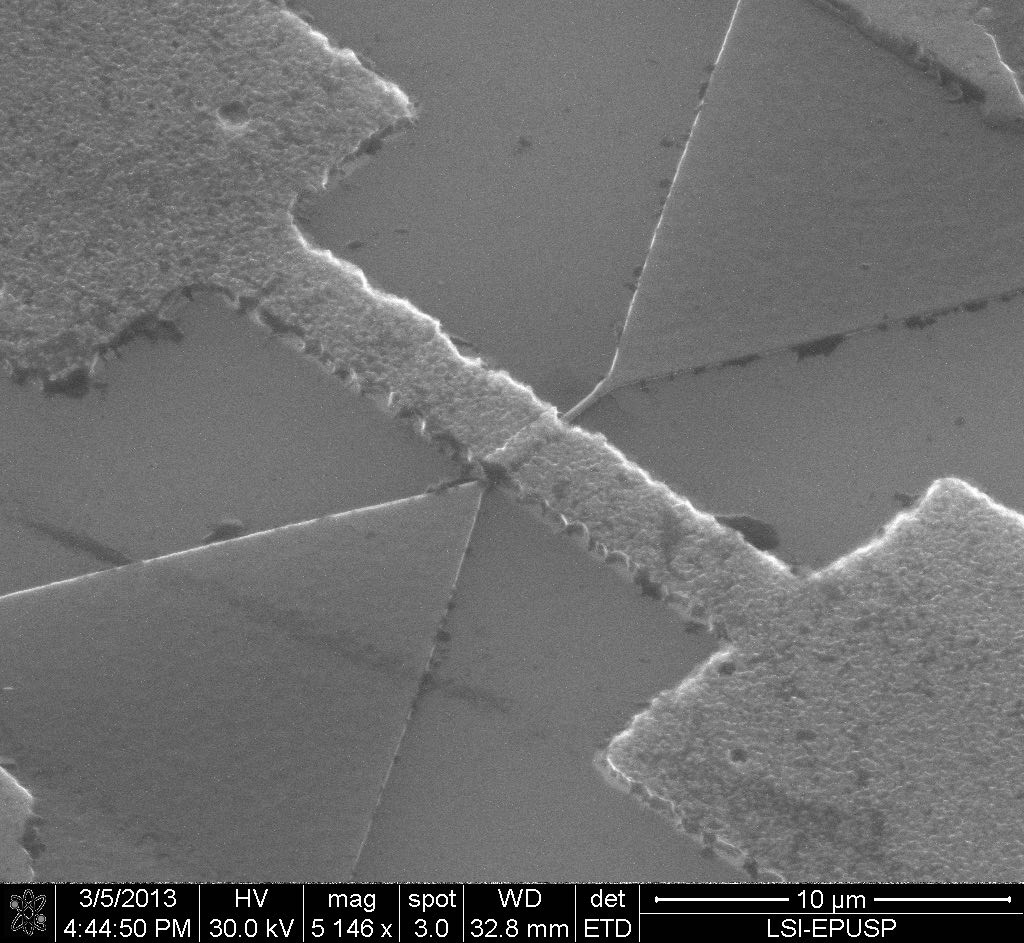

O curso apresenta uma abordagem prática e abrangente sobre a fabricação de circuitos integrados MOS em tecnologia SOI. Nesse contexto, os estudantes participam (em Sala Limpa) da sequência completa de fabricação de um Circuito integrado (CI) teste com transistores, diodos, capacitores e inversores, e se envolvem na pratica, com processos de fotolitografia, oxidação, implantação iônica, difusão térmica e deposição por plasma de filmes isolantes e metálicos. O curso também inclui aulas relativas ao projeto do processo de fabricação e caracterização elétrica dos dispositivos fabricados.

TECNOLOGIA UTILIZADA

A tecnologia SOI MOSFET é sucessora da tecnologia MOS convencional e na atualidade é padrão de fabricação nas principais indústrias de microeletrônica do mundo, como a Samsung, IBM e STMicroelectronics. Os dispositivos SOI fabricados no curso são de tipo nMOSFET e apresentam como principal característica a utilização de portas auto alinhadas de silício policristalino, num processo de fabricação que emprega apenas 3 etapas de fotolitografia. O processo em questão foi totalmente desenvolvido na Universidade de São Paulo (USP) e as aulas serão realizadas nas dependências do Laboratório de Microeletrônica (LME) e Laboratório de Sistemas Integráveis (LSI) da Escola Politécnica (EP) da USP. A tecnologia apresentada permite a fabricação de transistores SOI nMOSFET de até 0,5 mm.

PUBLICO ALVO

Profissionais da indústria,

Pesquisadores de centros de pesquisa em áreas afins com a microeletrônica e suas tecnologias,

Alunos de graduação e pós-graduação em Eng. Elétrica, Física e Química